The final PCI Express 6.0 specifications are a few months away, but the final draft, released about 5 months ago, allows chip designers and other companies to start introducing cutting-edge technology into their products: new features will no longer be added or changed. Synopsys, for example, has already unveiled the industry’s first full IP PCIe 6.0 solution that allows chip designers to integrate an advanced interface into their 5nm chips.

Synopsys DesignWare IP for PCIe 6.0 includes a controller (with Synopsys interface or optional ARM AMBA 5/4/3 AXI interfaces), physical interface (PHY), and Verification blocks. The solution provided by Synopsys allows chip designers to add a controller and physical interface to their 5nm design, and then verify that everything is working correctly.

Developers of ASICs for AI and HPC, GPUs, SSD controllers and other products that are sensitive to bandwidth and take advantage of the bandwidth that PCIe 6.0 can provide are interested in the latest interface. We are talking about speeds up to 128 GB / s via x16 interface in each direction. This means that, in theory, a PCIe 6.0-capable device can exchange 256GB of data per second.

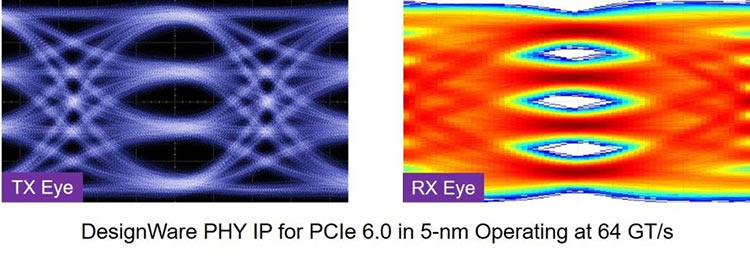

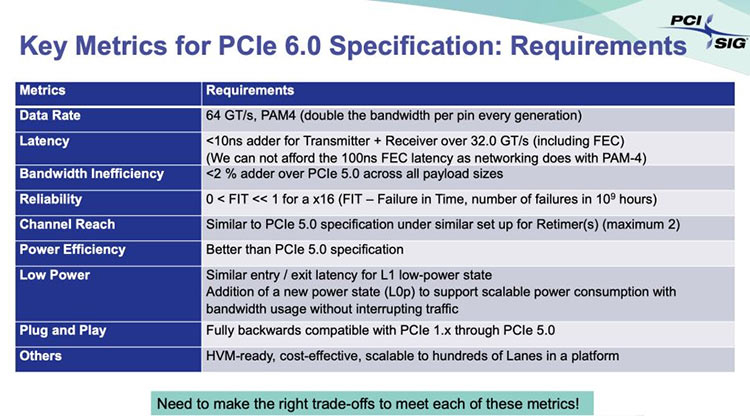

The PCIe 6.0 controller from Synopsys, in full compliance with the standard, increases the data transfer rate to 64 Gt / s versus 32 GT / s for PCIe 5.0 and 16 GT / s for PCIe 4.0. The signal structure of the interface uses a Pulse Amplitude Modulation (PAM4) transmission scheme instead of a no-return-to-zero (NRZ) pulse train transmission. Signal gradation with four levels will be used for transmission, which will increase the data transmission density and channel capacity. That being said, Synopsys claims to use an optimized data link to deliver ultra-low latency.

Other PCIe 6.0 features are also supported, such as Low Latency Forward Error Correction (FEC), FLIT mode, and L0p low power mode, all of which are key innovations in PCIe 6.0. On top of that, the Synopsys DesignWare PCIe 6.0 controller also supports proprietary adaptive DSP algorithms that optimize analog and digital stabilization to reduce power consumption by 20% at the interfaces between chips, riser and motherboard.

In the last 1,5 years, M.2 video cards, processors and solid-state drives have acquired support for PCIe 4.0. It will be some time before PCIe 5.0 support appears in leading products, but it’s nice to know that PCI-SIG has almost completed the development of the next version of the interface. PCIe 6.0 hardly makes sense in the consumer market today, but bandwidth is never too much in data centers. However, years later, PCIe 6.0 will certainly reach ordinary users.

If you notice an error, select it with the mouse and press CTRL + ENTER.