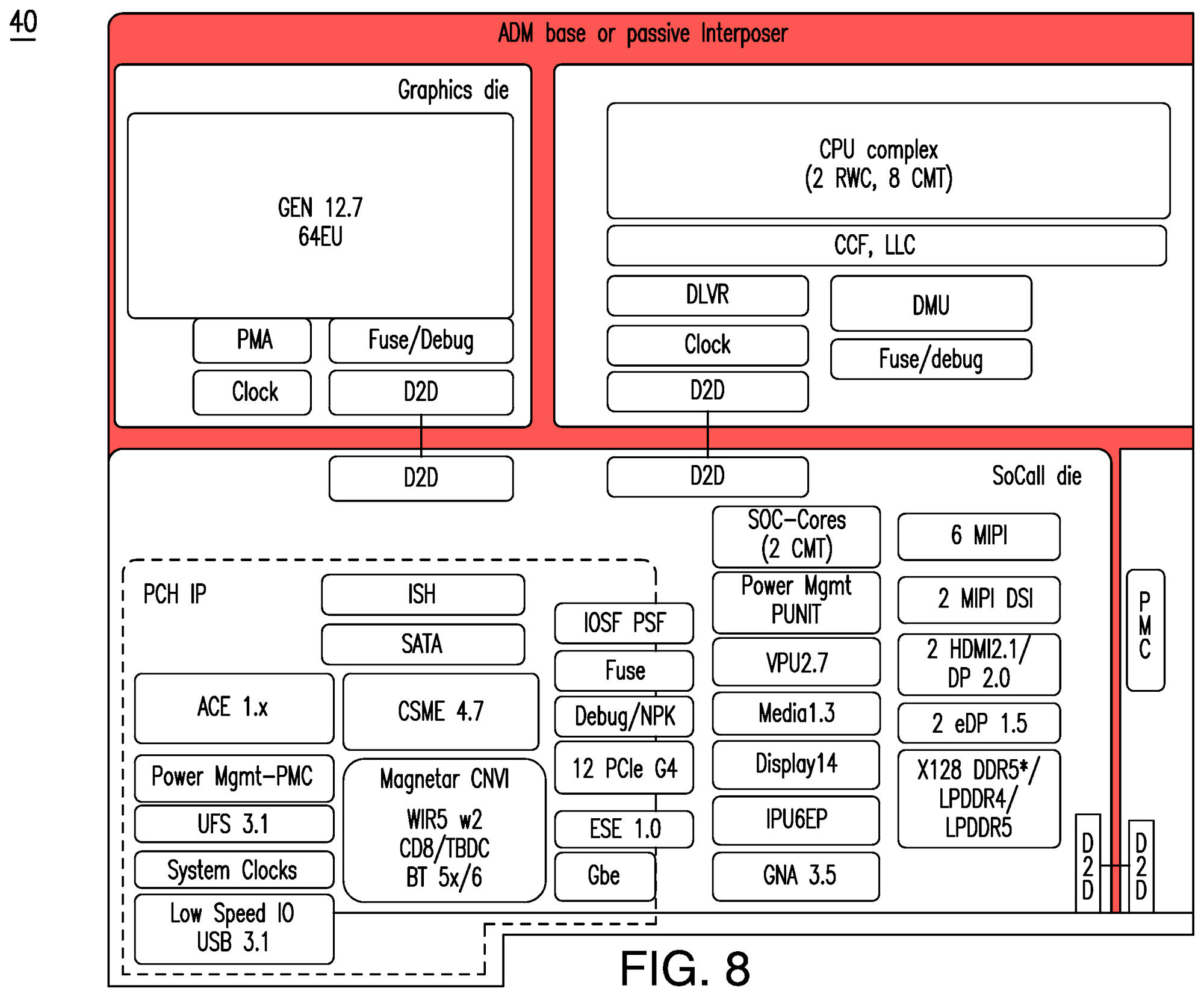

We recently wrote that Intel might equip Meteor Lake processors with L4 cache. The information confirms a patent dated 2020. Of the two versions of the location of the cache, the one that spoke about its location on the common base plate “won”. The name “Adamantine” or “ADM” was also confirmed.

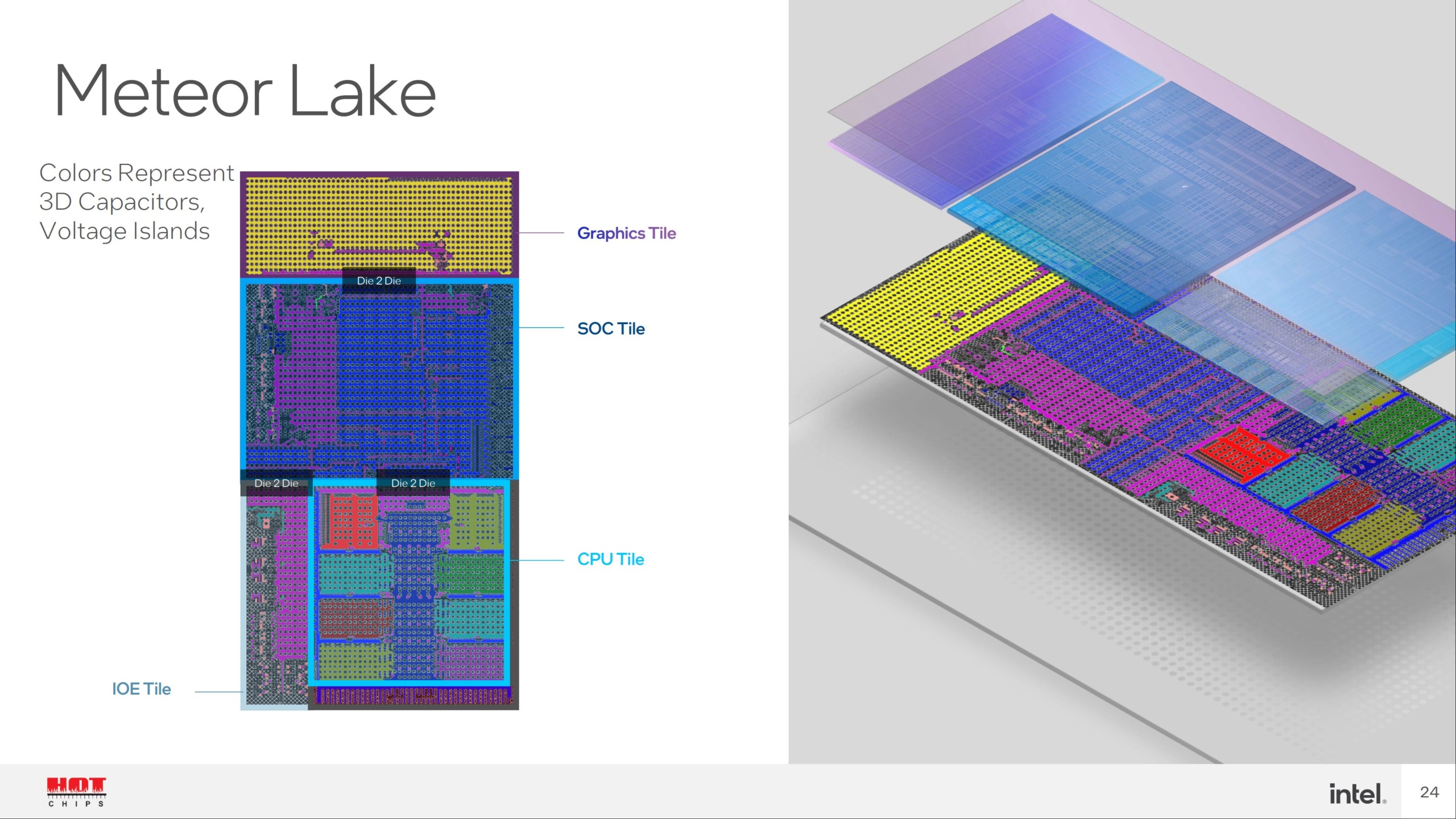

The patent states that the next-generation SoC architecture will receive on-package cache. This arrangement gives other blocks equal access to memory. We remind you that in addition to L4, the Meteor Lake motherboard will carry CPU, SoC, GPU and I/O chips. For all parts of the processor, this is faster access to the cache than to L3, which is part of the CPU.

The goals of the introduction of the L4 cache memory Intel calls the optimization of loading and increasing the security of the processor. L4 will keep the cache during the reset, which will reduce the download time.

Attached to the patent is a block diagram confirming the layout of Meteor Lake with 2 RWC cores (Redwood Cove) and 8 CMT cores (Crestmont). Interestingly, the SOC tile also carries two CMT cores, as mentioned in early leaks. This particular design will also get a Gen 12.7 Xe schedule with 64 EU.

Moore’s Law Is Dead has previously hinted at a possible cache size of up to 1GB, claiming that 128MB to 512MB are currently being tested. The launch of Intel Meteor Lake is expected in the second half of 2023, but it is not known which modification will be released at that time.

Processor rumors: AMD Zen 6 on the 2nm process and L4 cache in Intel Core 14th generation (Meteor Lake)

Course

Microservice architecture

Source: VideoCardz